Memory compiler saves power for IoT

A 40nmULP memory compiler facilitates use of sureCore’s 40nm low voltage SRAM IP that effectively operates at a record-setting 0.6V across process voltage and temperature.

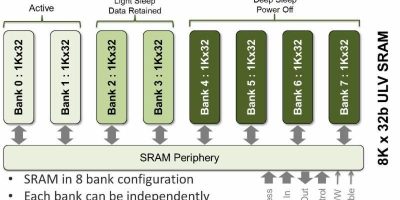

The compiler supports synchronous single port SRAM with operating voltages ranging from 0.6 to 1.21V and memory capacities ranging from 8.0 to 576kbyte with maximum word lengths of 72bits. Previous test chip results revealed up to 80% savings in dynamic power consumption and up to 75% reduction in static power.

The design targets power-critical, always on IoT, wearable and medical applications. The SRAM is single rail- and DVFS-compatible. Power management options include light sleep, deep sleep and power-down modes. The array is sub-divided into up to eight banks that can be in independently active, retained or powered off modes. The compiler also provides Design-for-Test (DFT) and BIST support.

WEARTECHDESIGN.COM – Latest News/Advice on Technology for Wearable Devices

Weartechdesign is unlike any other website currently serving the technology

for wearable devices. We carry the very latest news for design engineers and purchasers.

Register on our mailing list to receive regular updates and offers from

WearTechDesign